シリアル・ペリフェラル・インタフェース, by Wikipedia https://ja.wikipedia.org/wiki?curid=1015608 / CC BY SA 3.0

#インタフェース規格

#物理層プロトコル

SPIバスでの接続の例 SPIバスでの複数デバイスの接続の例 シリアル・ペリフェラル・インタフェース(Serial Peripheral Interface, SPI)は、コンピュータ内部で使われるデバイス同士を接続するバスである。

パラレルバスに比べて接続端子数が少なくて済むシリアルバスの一種で、比較的低速なデータ転送を行うデバイスに利用される。

従来のデータバス、アドレスバス、制御信号による周辺デバイスの接続には、少なくとも十数本の信号を接続する必要があった。

メインメモリなどの高速にアクセスできる必要があるデバイスを除いて、それほど速度を必要とされないデバイスに関しては、ICのパッケージも小型化できることから、省ピンで接続できる形態が望まれた。

このような背景から、いくつかのシリアルバス規格が提唱された。

(I2C, SPI, MicroWireなど) SPIは省ピンで接続できるバスとして、モトローラ(現在はNXPセミコンダクターズ)が提唱した規格である。

信号線は4本で構成され、一つのデバイスを接続する場合はSSを固定することで3本で接続できる。

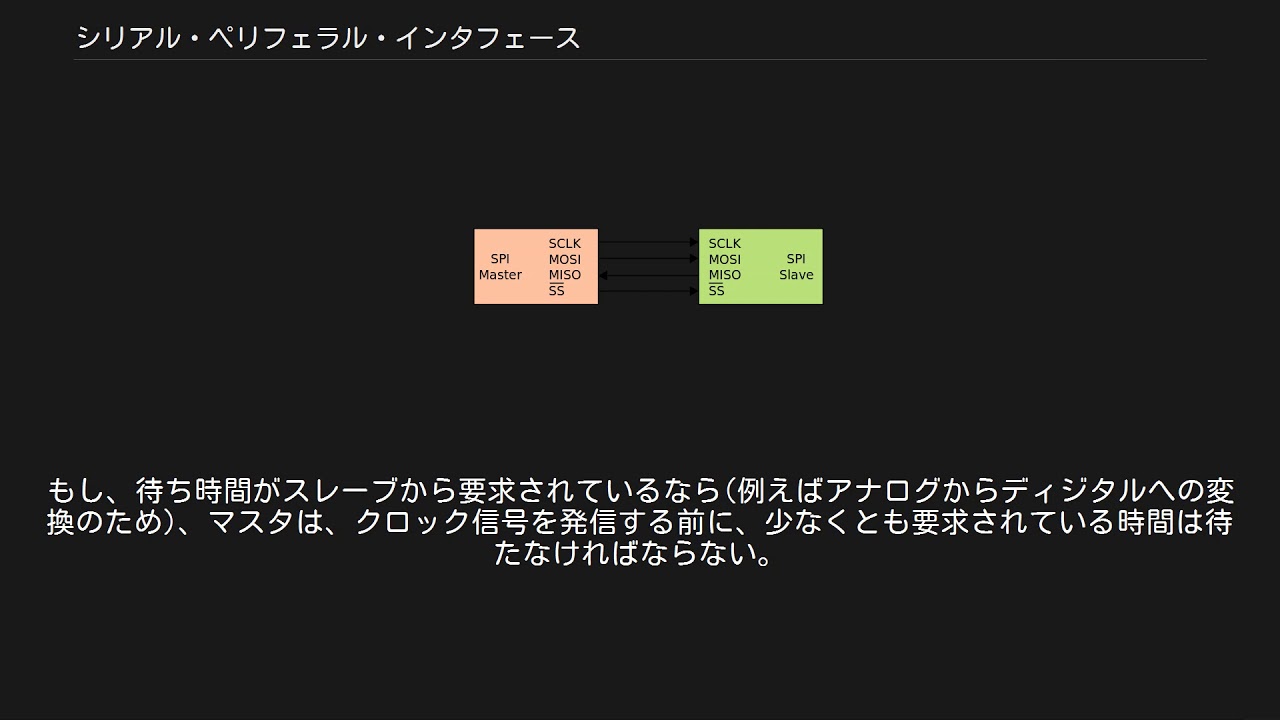

SCK Serial Clock MISO Master In Slave Out MOSI Master Out Slave In SS Slave Select SPIバスは、単一のマスタと、1つ以上のスレーブの装置で操作することができる。

もし、スレーブの装置が単一であり、スレーブの装置が許可するなら、SSピンは論理レベルをLowに固定してもよい。

ただし、ある種のスレーブは、Slave Select信号の立下りのエッジを、動作開始のために必要とするので、固定できない場合がある。

例えば、Maxim MAX1242 ADCであり、high→lowへの遷移で変換開始する。

複数のスレーブ装置を使うには、マスターからそれぞれのスレーブへの独立したSS信号線が要求される。

ほとんどのスレーブ装置は、tri-state outputを持ち、デバイスが選択されていない時のMISO信号は、high impedance (電気的に切断状態)になる。

tri-state 出力を持たない装置は、外部tri-state バッファを用いない限り、SPIを他の装置と共用する事ができない。

典型的なハードウェア構成。

2つのシフトレジスタが、チップ間のリングバッファを形成する 通信を始めるために、マスタは、スレーブがサポートする周波数(典型的には数MHz)のクロック信号を生成する。

その後、マスタは該当するスレーブのSS線の論理レベルを0にして、スレーブを選択する。

もし、待ち時間がスレーブから要求されているなら(例えばアナログからディジタルへの変換のため)、マスタは、クロック信号を発信する前に、少なくとも要求されている時間は待たなければならない。

SPIの各クロックの間に、全二重データ送信が行われる。

マスタはMOSI線上で1ビットを送信し、スレーブがそれを読み込む。

その間、スレーブはMISO線上で1ビット送信し、マスタがそれを読み込む。

この一連の処理は、たとえ一方通行のデータ送信を目的としていても維持される。

通常、送信には、8ビットなど、特定のワードサイズの2つのシフトレジスタが用いられる。

1つはマスターに、もう1つはスレーブに配置される。

これらのレジスタは、仮想的なリング状に接続される。

データは通常、最上位ビットが最初にシフトアウトされます。

クロックエッジで、マスターとスレーブの両方がビットをシフトアウトし、伝送ライン上で向かい合う相手に出力します。

次のクロックエッジで、各レシーバーで伝送ラインからビットがサンプリングされ、シフトレジスタの新しい最下位ビットとして設定されます。

レジスタの全ビットがシフトインおよびシフトアウトされた後には、マスターとスレーブはレジスタ値を交換した状態になります。

さらにデータを交換する必要がある場合、シフトレジスタがリロードされ、この一連の処理が繰り返されます。

送信は、任意の数のクロックサイクルにわたって継続できます。

完了すると、マスターはクロック信号のLowとHighの切り替えを停止し、通常はスレーブの選択を解除します。

多くの場合、送信は8ビットワードで構成されます。

ただし、他のワードサイズも一般的です。

たとえば、Texas InstrumentsのTSC2101などのタッチスク…

Comments