Alpha 21264, by Wikipedia https://ja.wikipedia.org/wiki?curid=2580939 / CC BY SA 3.0

#スーパースカラー・マイクロプロセッサ

#DECのマイクロプロセッサ

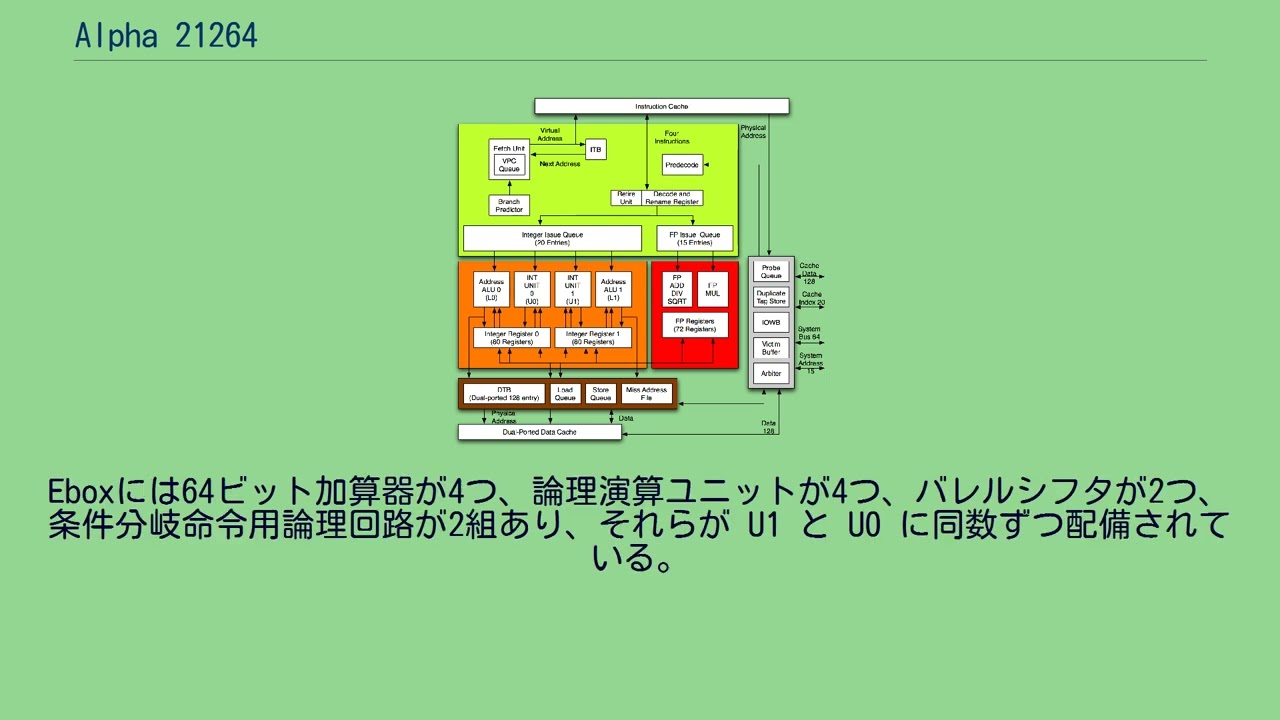

Alpha 21264 のマイクロアーキテクチャ Alpha 21264 はディジタル・イクイップメント・コーポレーション (DEC) が開発・製造したRISCマイクロプロセッサであり、Alpha命令セットアーキテクチャ (ISA) を実装している。

コード名 EV6 でも知られている。

1996年10月に登場した。

Alpha 21264 はクロックサイクル毎に最大4個の命令を同時発行できるスーパースケーラ型マイクロプロセッサであり、アウト・オブ・オーダー実行と投機的実行を実装している。

最大6命令を同時に実行できる。

命令パイプラインは7段構成。

同時代の他のマイクロプロセッサをしのぎ、複数のパイプラインの各ステージを合わせると、最大80個の命令を同時に処理する能力を有する。

デコードした命令を命令キュー群にキューイングし、オペランドが利用可能となった命令から発行する。

整数命令キューには20命令、浮動小数点命令キューには15命令まで蓄えることができる。

それぞれのキューは対応するパイプライン群と同数の命令を発行できる。

Eboxは整数演算命令、ロード/ストア命令を実行する。

2つの整数演算ユニットと2つのロード/ストアユニットと2つの整数レジスタファイルを持つ。

整数レジスタファイルはそれぞれ80エントリで、うち31本はアーキテクチャ上のレジスタ、41本はレジスタ・リネーミング用、8本はPALcode用レジスタである。

R31レジスタは常にゼロなので、レジスタファイル内のエントリを使っていない。

レジスタファイルはそれぞれ、整数演算ユニット1つとロード/ストアユニット1つに対応しており、それら3つをまとめて「クラスタ」と称する。

2つのクラスタをそれぞれ U0 および U1 と呼ぶ。

このような構成になっているのは、レジスタファイルのリードおよびライトのポート数を削減するためであり、結果としてレジスタファイルに必要なチップ面積を低減し、高クロック周波数での動作を可能とする。

まるでマルチコアのような構成だがマルチコアではないので、レジスタファイルへの書き込みは常に同期を必要とし、結果として1%の性能ペナルティを生ずる。

この性能ペナルティを補償するため、第一により高いクロック周波数で動作させ、第二にもう一方のクラスタが使用中のレジスタをオペランドとして必要とする命令を発行機構が発行しないようにして依存関係が発生するのを防いでいた。

2つのクラスタには2つの違いがある。

U1には7サイクルのパイプライン化乗算器があり、U0にはマルチメディア拡張 (MVI) 命令用の3サイクルのパイプラインがある。

MVIは Alpha ISA のSIMD命令拡張である。

ロード/ストアユニットは、メモリアクセスのための実効アドレス(仮想アドレス)を計算する単純な演算装置を含んでいる。

これを単純な算術命令や論理命令の実行にも使用することができる。

命令発行機構はこれを考慮しており、アドレス計算をしていない状態であればロード/ストアユニットに対してロード/ストア命令以外の命令も発行する。

Eboxには64ビット加算器が4つ、論理演算ユニットが4つ、バレルシフタが2つ、条件分岐命令用論理回路が2組あり、それらが U1 と U0 に同数ずつ配備されている。

Fboxは浮動小数点演算命令を実行する。

2つの浮動小数点演算パイプラインと1つの浮動小数点レジスタファイルがある。

2つのパイプラインは同一ではなく、加算パイプラインは乗算以外のあらゆる浮動小数点命令を実行し、もう1つは乗算命令専用である。

加算パイプラインにはパイプライン化されていない浮動小数点除算ユニットと平方根ユニットが接続されている。

加算や乗算など多くの命令のレイテンシは4サイクルで、倍精度除算のレイテンシは16サイクル、単精度除算のレイテンシは33サイクルである。

浮動小数点レジスタファイルは72エントリで、うち32本がアーキテクチャ上のレジスタ、残り40本はレジスタ・リネーミング用である。

キャッシュは一次と二次の2レベル構成である。

Alpha 21164 の3レベル・キャッシュ構成は帯域幅に問題があるため採用されなかった。

分岐予測には統合分岐予測アルゴリズムを採用している。

このアルゴリズムはDECの Western Research Laboratory (WRL) の Scott McFarling が開発したもので、1993年…

Comments